# intel

## Itanium<sup>™</sup> Processor Floatingpoint Software Assistance and Floating-point Exception Handling

January 2000

Order Number: 245415-001

## intel

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Itanium<sup>™</sup> processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copyright © Intel Corporation, 2000

\*Third-party brands and names are the property of their respective owners.

# int<sub>e</sub>l。 *Contents*

| 1 | Introdu                                                                                             | ction                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-1                                                                                       |

|---|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|   | 1.1<br>1.2                                                                                          | Related Documents<br>Software Components Supporting Floating-point Exception Handling                                                                                                                                                                                                                                                                                                                                                                       |                                                                                           |

| 2 | Softwar                                                                                             | re Assistance Faults and Traps on the Itanium™ Processor                                                                                                                                                                                                                                                                                                                                                                                                    | 2-1                                                                                       |

|   | 2.1<br>2.2<br>2.3<br>2.4                                                                            | Architecturally Mandated SWA Faults<br>Itanium™ Processor-specific SWA Faults<br>Itanium™ Processor-specific SWA Traps<br>Handling Floating-point Exceptions                                                                                                                                                                                                                                                                                                | 2-1<br>2-1                                                                                |

| 3 | Conditio                                                                                            | ons Causing, and Responses to, Floating-point Exceptions                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1                                                                                       |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14 | The Floating-point Status Register<br>The Interruption Status Register<br>Floating-point Exception Priority<br>Conditions Causing Floating-point Exceptions on the Itanium <sup>™</sup> Processor<br>Response to SWA Faults<br>Response to Invalid Faults<br>Valid Operations with NaNs<br>Response to Divide-by-Zero Faults<br>Response to Denormal Faults<br>Response to SWA Traps<br>Response to Overflow Traps<br>Response to Inexact Traps<br>Examples | 3-3<br>3-4<br>3-9<br>3-14<br>3-20<br>3-22<br>3-23<br>3-24<br>3-24<br>3-25<br>3-26<br>3-27 |

| 4 | Archite                                                                                             | cturally Mandated Floating-point Software Assistance                                                                                                                                                                                                                                                                                                                                                                                                        | 4-1                                                                                       |

|   | 4.1                                                                                                 | <ul> <li>Conditions that Require Architecturally Mandated SWA</li> <li>4.1.1 Architecturally Mandated SWA Conditions for Divide</li> <li>4.1.2 Architecturally Mandated SWA Conditions for Square Root</li> <li>4.1.3 Floating-point Traps Raised by the SWA Handler for</li> </ul>                                                                                                                                                                         | 4-1<br>4-3                                                                                |

|   | 4.2<br>4.3                                                                                          | Architecturally Mandated SWA Faults<br>Algorithms for SWA Faults for Floating-point Divide<br>Frequency Estimation of the Architecturally Mandated SWA Faults for<br>Floating-point Divide                                                                                                                                                                                                                                                                  | 4-5                                                                                       |

|   | 4.4<br>4.5                                                                                          | Algorithms for SWA Faults for Floating-point Square Root<br>Frequency Estimation of the Architecturally Mandated SWA Faults for<br>Floating-point Square Root                                                                                                                                                                                                                                                                                               |                                                                                           |

| 5 |                                                                                                     | cturally Mandated Pseudo-SWA Requests for<br>I Computations                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1                                                                                       |

|   | 5.1<br>5.2                                                                                          | Architecturally Mandated Pseudo-SWA Conditions for Parallel<br>Floating-point Divide<br>Frequency Estimation of the Architecturally Mandated Pseudo-SWA                                                                                                                                                                                                                                                                                                     | 5-1                                                                                       |

|   | 5.3                                                                                                 | Faults for Parallel Floating-point Divide<br>Architecturally Mandated Pseudo-SWA Conditions for Parallel                                                                                                                                                                                                                                                                                                                                                    |                                                                                           |

|   | 5.4                                                                                                 | Floating-point Square Root<br>Frequency Estimation of the Architecturally Mandated Pseudo-SWA<br>Faults for Parallel Floating-point Square Root                                                                                                                                                                                                                                                                                                             |                                                                                           |

## intel®

| 6 | Exampl     | es                                                                                                                                                                                                                                                                                                                                                                                          | 6-1               |

|---|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|   | 6.1        | <ul> <li>Examples of Itanium<sup>™</sup> Processor-specific Software Assistance Requests</li> <li>6.1.1 Itanium<sup>™</sup> Processor-specific Software Assistance Faults</li> <li>6.1.2 Itanium<sup>™</sup> Processor-specific Software Assistance Traps</li> <li>6.1.3 Sample Code for Examples of Itanium<sup>™</sup> Processor-specific Software Assistance Faults and Traps</li> </ul> | 6-1<br>6-5<br>6-8 |

|   | 6.2        | Examples of IA-64 Architecturally Mandated Software Assistance Requests .6                                                                                                                                                                                                                                                                                                                  | -11               |

| 7 | Implem     | entation of the IA-64 Floating-point Emulation Library                                                                                                                                                                                                                                                                                                                                      | 7-1               |

|   | 7.1        | EFI Floating-point SWA Driver<br>7.1.1 EFI Drivers<br>7.1.2 FP SWA EFI Driver<br>7.1.3 OS Loader / OS Initialization Requirements                                                                                                                                                                                                                                                           | 7-1<br>7-2        |

|   | 7.2<br>7.3 | Floating-point SWA Handler API - API for the IA-64 Floating-point<br>Emulation Library<br>Integration with the Operating System                                                                                                                                                                                                                                                             | 7-5               |

| 8 | Referer    | nces                                                                                                                                                                                                                                                                                                                                                                                        | 8-1               |

## Figures

| 1-1 | Flow of Control for IA-64 Floating-point Exceptions                    | 1-3 |

|-----|------------------------------------------------------------------------|-----|

| 3-1 | Floating-point Status Register (AR40)                                  | 3-3 |

| 3-2 | Interruption Status Register Code (ISR.code) from ISR (CR17)           | 3-4 |

| 3-3 | Exception Priority for Itanium™ Processor Floating-point Faults        | 3-6 |

| 3-4 | Exception Priority for Itanium™ Processor Floating-point Traps         |     |

|     | Generated by a Hardware Initiated Computation of the Result            | 3-7 |

| 3-5 | Exception Priority for Itanium™ Processor Floating-point Traps         |     |

|     | Generated by a Software Initiated Computation of the Result            | 3-8 |

| 3-6 | Flow of Control for Handling a SWA Fault Raised by a Divide            |     |

|     |                                                                        | -28 |

| 3-7 | Flow of Control for Handling a Double Fault (V high, SWA               |     |

|     | Fault low), Raised by an IA-64 Parallel Instruction 3-                 | -29 |

| 3-8 | Flow of Control for Handling a Fault in the High Half (V high),        |     |

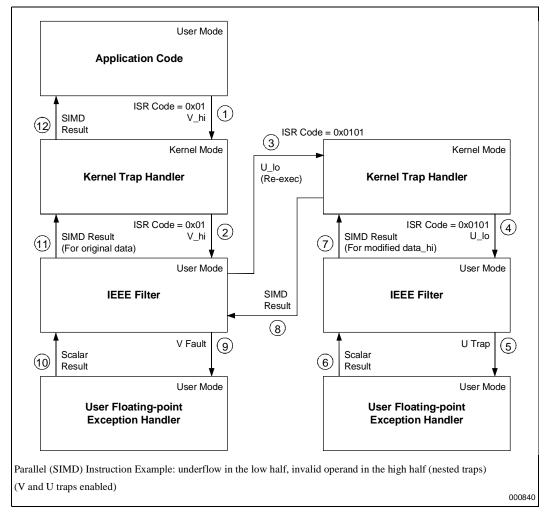

|     | and a Trap in the Low Half (U low) of an IA-64 Parallel Instruction 3- | -30 |

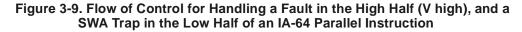

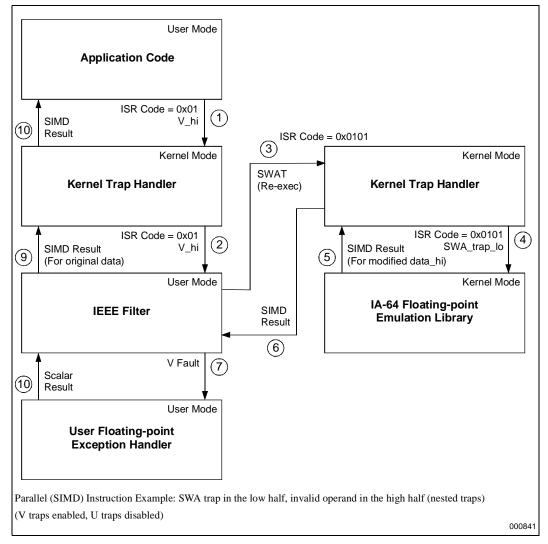

| 3-9 | Flow of Control for Handling a Fault in the High Half (V high),        |     |

|     | and a SWA Trap in the Low Half of an IA-64 Parallel Instruction        |     |

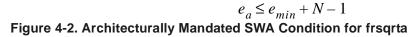

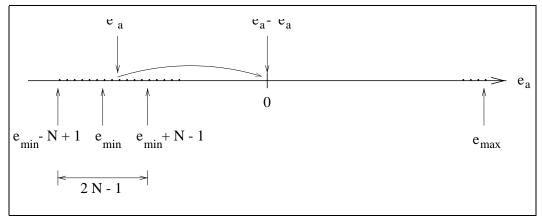

| 4-1 | Architecturally Mandated SWA Conditions for frcpa                      |     |

| 4-2 | Architecturally Mandated SWA Condition for frsqrta 4-                  | -19 |

## intel

## Tables

| 3-1  | Itanium <sup>™</sup> Processor Arithmetic Instructions and Floating-point |      |

|------|---------------------------------------------------------------------------|------|

|      | Exceptions which may be Raised                                            | 3-1  |

| 3-2  | Conditions that Determine Occurrence of Floating-point Exceptions         | 3-9  |

| 3-3  | Response of the IA-64 Arithmetic Instructions to SWA Faults               | 3-14 |

| 3-4  | Masked Response of the IA-64 Arithmetic Instructions to Invalid           |      |

|      | Exceptions (listed in decreasing order of their priority)3-21             |      |

| 3-5  | Result of Floating-point Arithmetic Instructions for QNaN Input(s),       |      |

|      | in the Absence of Floating-point Exceptions                               | 3-23 |

| 3-6  | Masked Response of the IA-64 Arithmetic Instructions to                   |      |

|      | Divide-by-Zero Exceptions                                                 | 3-23 |

| 3-7  | Response of the IA-64 Arithmetic Instructions to Itanium <sup>™</sup>     |      |

|      | Processor-specific SWA Traps                                              | 3-24 |

| 3-8  | Response of the IA-64 Arithmetic Instructions to Overflow Exceptions      | 3-25 |

| 3-9  | Response of the IA-64 Arithmetic Instructions to Underflow Exceptions     | 3-26 |

| 3-10 | Response of the IA-64 Arithmetic Instructions to Inexact Exceptions       | 3-27 |

## intel®

This document describes the details regarding Floating-point Software Assistance exceptions (FP SWA requests) in particular, and floating-point exceptions in general on the Itanium<sup>™</sup> processor, the first implementation of the IA-64 architecture. The document is useful to operating system writers and compiler writers, besides being useful to anyone who wants to obtain a better understanding of floating-point exceptions in the IA-64 architecture. Chapter 1 through Chapter 3 contain the general background information, while Chapter 4 through Chapter 7 are more focused, and go into a lower level of detail. Chapter 7 gives the information necessary in integrating the FP SWA Handler (the FP SWA EFI driver) with the operating system.

Chapter 1 contains the introduction and describes the software components of an operating system supporting floating-point exception handling.

Chapter 2 describes the Software Assistance (SWA) traps and faults on the Itanium processor, and

Chapter 3 lists the conditions causing floating-point exceptions, the floating-point exception priorities (distinguishing between exceptions raised [signaled] directly by the hardware and exceptions raised by the software), and specifies the response of the various Itanium processor instructions to floating-point exceptions - for both disabled (masked) and enabled (unmasked) exceptions.

Chapter 4 discusses the IA-64 architecturally mandated Software Assistance requests, which can be raised only by the divide and square root reciprocal approximation instructions (frcpa and frsqrta). The floating-point divide and square root operations (as well as other operations based on them, such as remainder, or integer divide and remainder) are implemented in software in the IA-64 architecture. The starting point which is provided by the reciprocal approximation instructions is followed by instructions that implement Newton-Raphson based or similar algorithms for divide and square root or their derivatives. Software assistance is required when the reciprocal approximation instructions implemented in hardware are not able to provide an initial value sufficient for the software algorithms to determine the IEEE correct results for divide or square root. Alternate algorithms are used when such requests are made by the hardware. The frequency of occurrence for software assistance requests is estimated in Section 4.3 and Section 4.5.

Chapter 5 examines the architecturally mandated Pseudo-Software Assistance requests, characteristic for the parallel divide and square root reciprocal approximation instructions. These requests are raised in situations similar to those for the scalar divide and square root reciprocal approximation instructions, but instead of leading to a SWA fault or trap, the output predicate of the parallel reciprocal approximation instruction is cleared. The frequency of occurrence for the pseudo-software assistance requests is estimated in Section 5.2 and Section 5.4.

Chapter 6 gives examples of software assistance requests. Examples of Itanium processor specific SWA requests are given first, followed by IA-64 architecturally mandated requests.

Chapter 7 describes the implementation of the software component that handles software assistance requests - the IA-64 Floating-point Emulation Library, and specifies the API that allows this library supported by Intel to be shared by various operating systems. The IA-64 Floating-point Emulation Library (which has the role of a Floating-point SWA Handler) is implemented as an EFI (Extensible Firmware Interface) driver.

Chapter 8 contains the references used in the text.

#### 1.1 Related Documents

The IA-64 floating-point architecture and operations are discussed in several other documents. Information contained in these sources is useful, or helpful when reading the present document. The main source of information is the Intel IA-64 Architecture Software Developer's Guide [1]. Information specific to the Intel architecture can also be found in [2].

The recommended source for reference information on floating-point exceptions is the IEEE Standard 754-1985 for Binary Floating-point Computations [3].

#### 1.2 Software Components Supporting Floating-point Exception Handling

Floating-point exception handling in the IA-64 architecture has new features compared to IA-32 [2]. First, the IA-64 floating-point architecture is more complex than that of previous Intel processors. There are new instructions, some with three input operands, static precision modes (e.g. in fma.s), static rounding modes (e.g. in fcvt.fx.trunc), and new floating-point formats and computation models. Second, the necessity for software assistance (SWA) is new in the Intel Architecture, and augments the floating-point exception handling mechanism. Third, the IA-64 architecture also has the ability to handle new parallel floating-point instructions. On the other hand, the IA-64 architecture has extended floating-point capabilities, both in performance and in accuracy.

When a floating-point exception occurs, the hardware saves a minimal amount of processor state information in interruption control registers (only the registers of interest for floating-point exceptions are listed): IPSR (CR16 - Interruption Processor Status Register), ISR (CR17 - Interruption Status Register), IIP (CR19 - Interruption Instruction Bundle Pointer), IIPA (CR22 - Interruption Instruction Previous Address), and IFS (CR23 - Interruption Function State). The information in IIP, IPSR, and IFS is saved only if PSR.ic is set to 1. The information in IIPA is saved only if PSR.ic was 1 prior to the interruption. Finally, ISR is saved regardless of the value of PSR.ic.

A branch to the interruption vector (Floating-point Fault Vector 0x5c00 or Floating-point Trap Vector 0x5d00) and then to a low-level OS handler allows saving more of the processor state, and propagates handling of the task higher in the operating system.

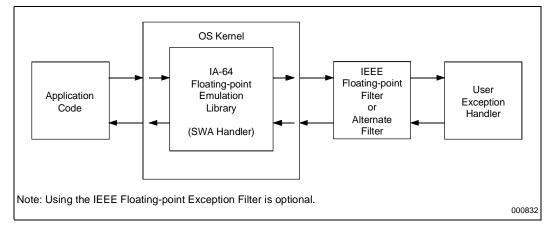

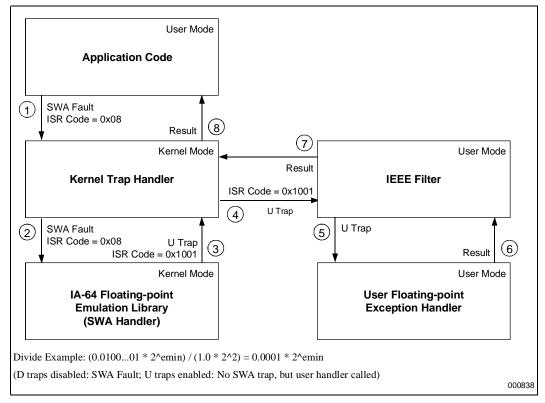

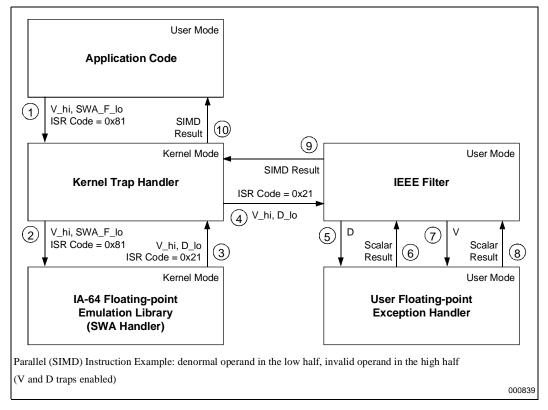

On any platform based on an IA-64 processor, two system-level components are used in floating-point exception handling: the operating system kernel floating-point trap handler, and the IA-64 Floating-point Emulation Library (FP SWA Handler). The kernel floating-point trap handler has the role to save state information not saved by the processor, and then to invoke the appropriate exception handler: the FP SWA Handler for FP SWA requests, or the FP SWA handler and then a user-level floating-point exception handler for other unmasked (enabled) floating-point exceptions.

Figure 1-1 depicts the control flow that occurs when an application running on an IA-64 processor causes a floating-point exception condition.

The IA-64 Floating-point Emulation Library (implemented as an EFI driver invoked by the OS kernel) is capable of emulating any floating-point instruction defined by the architecture. It handles the cases that require software assistance — situations that the hardware cannot handle, which fall into the three categories presented in the next subsection.

## intel

#### Figure 1-1. Flow of Control for IA-64 Floating-point Exceptions

Introduction

## intel

## int<sub>el</sub>.

## Software Assistance Faults and Traps on the Itanium<sup>™</sup> Processor

The three categories of Software Assistance exceptions: IA-64 architecturally mandated SWA faults, Itanium processor specific SWA faults, and Itanium<sup>TM</sup> processor specific SWA traps, are presented next.

#### 2.1 IA-64 Architecturally Mandated SWA Faults

The architecturally mandated SWA faults occur for the scalar reciprocal approximation instructions, *frcpa* and *frsqrta*, when their input operands are such that they potentially prevent generation of the correct results by the iterative software algorithms that are employed for divide and square root. Alternate algorithms are implemented in the IA-64 Floating-point Emulation Library to provide the correct results in such situations.

In the case of the Itanium processor specific SWA exceptions (Section 2.2 and Section 2.3 below), the SWA fault or trap can be caused by both scalar or parallel instructions. The architecturally mandated SWA faults are caused only by scalar instructions (frcpa and frsqrta). The parallel counterparts of the reciprocal approximation instructions, *fprcpa* and *fprsqrta* just clear their output predicate (in situations in which the scalar instructions would raise SWA faults), expecting this to cause alternate algorithms to be executed in order to perform the parallel divide or square root operations.

#### 2.2 Itanium<sup>™</sup> Processor Specific SWA Faults

SWA faults are allowed in the IA-64 architecture for virtually any reason. The architecturally allowed SWA faults that occur on the Itanium processor are referred to as Itanium processor specific SWA faults, and they arise when floating-point instructions consume denormalized or unnormal operands. If the denormal exceptions are disabled (masked), the SWA fault is resolved by the IA-64 Floating-point Emulation Library (the SWA handler). If the denormal exceptions are enabled (unmasked), the SWA fault is converted to a denormal fault by the IA-64 Floating-point Emulation Library, and it is propagated through the OS kernel to the user level (a denormal fault exception handler must have been registered to handle it). As SWA faults may be raised for any reason in an IA-64 Architecture implementation in general, the IA-64 Floating-point Emulation Library was designed and implemented to be able to provide the correct result for any IA-64 floating-point arithmetic instruction, and for any values of the input operands.

#### Itanium<sup>™</sup> Processor Specific SWA Traps 2.3

SWA traps are allowed in the IA-64 architecture when:

- Tiny results are generated and the underflow traps are disabled.

- Huge results are generated and the overflow traps are disabled.

- Inexact results are generated and the inexact traps are disabled.

Note that tiny numbers have non-zero values, but less in absolute value than the smallest positive normal floating-point number. Huge numbers have values larger in absolute value than the largest positive normal floating-point number. The result of a floating-point operation is evaluated for tininess or hugeness after rounding to the destination precision, but assuming an unbounded exponent ("first IEEE rounding"), and before the second rounding that takes into account the limited exponent range ("second IEEE rounding"). Note though that these two rounding steps are hypothetical, and that the hardware only performs the IEEE rounding in one step (combining the two steps outlined above). Breaking it into two steps just helps understanding the way numeric results are generated. For tiny results, rounding will require denormalization, i.e. shifting the significand to the right, while incrementing the exponent in order to bring it into the range allowed by the format, followed by rounding to the destination precision. This has to be carried out on the infinitely precise result, and the rounded result may be zero, a denormal, or the smallest normal number representable in the destination format, with the appropriate sign (which means that the first rounding step is not necessary in this case). If the result is huge, the second rounding will modify it either to the largest normal floating-point number representable in the destination format, or to infinity (with the appropriate sign).

The Itanium processor specific SWA traps occur only when tiny results are generated, the underflow traps are disabled, and the flush-to-zero mode is not enabled.

#### 2.4 Handling Floating-point Exceptions

When a SWA request occurs, an instruction bundle is read, the excepting instruction is decoded, its input or output operands are read, a result is generated, and the processor state is modified by the software.

The IA-64 Floating-point Emulation Library provides a result only for SWA faults and traps. Exceptions are the cases when a SWA fault or trap generates a new floating-point exception, e.g. for an Itanium processor specific SWA faults, when the denormal exceptions are enabled (in which case the result is provided by a user handler for denormal exceptions). The library is invoked though for all the enabled (unmasked) floating-point exceptions (SWA or not). Three situations are possible.

The first possibility is for the emulation library to recognize a SWA fault or a SWA trap. It starts processing it, and if a result can be generated, it is passed back to the kernel floating-point trap handler, which in turn has to resume the thread that raised the exception.

The second possibility is for the emulation library to recognize an unmasked floating-point exception other than a SWA fault or trap, or to have to raise a new floating-point exception that occurs during the process of generating a result for the SWA fault or trap. This information is then returned to the kernel trap handler, which will have to propagate the exception to a user level floating-point exception handler.

The third possibility is for the emulation library to not recognize a floating-point fault or trap when called by the OS kernel (this may include the case when incorrect parameters were passed to it). In this situation, it returns to the OS kernel a value indicating failure, plus additional diagnostic information.

At the user level, the floating-point exception can be handled by a user handler directly, or by a filter function (usually an IEEE floating-point exception filter) that invokes a user handler.

The first function of an IEEE Floating-point Exception Filter is to transform the interruption information to a format that is easier to understand and handle by the user, and to invoke a user handler for the exception. The user provided result, and possibly other changes are propagated back into the processor state if execution is continued (in some programming environments, the

user has up to three options: to continue execution, to execute some cleanup code and exit, or to continue searching for another handler).

The second function of the filter is to hide the complexities of the parallel instructions from the user. If a floating-point fault occurs for example in the high half of a parallel floating-point instruction, and there is a user handler provided for that case, the parallel instruction is split into two scalar instructions. The result for the high half comes from the user handler, while the low half is re-executed. The two results are combined back into a parallel result, and execution can continue. More complicated cases are those when two faults and/or traps occur in the same instruction (the model used can be extended to more than 2-way parallel instructions). Note that usage of the IEEE Floating-point Exception Filter is not compulsory - the user may choose to handle enabled floating-point exceptions differently. A filter can be provided just as a convenient way to solve such situations. Still, at least a filter with reduced functionality is necessary in order to ensure full compliance with the IEEE-754 Standard requirements [6] regarding values to be passed to a user handler when a floating-point exception occurs (e.g. scaling of the hardware generated result when an overflow or underflow exception is raised has to be performed by the filter function).

The next chapter describes the IA-64 instructions that are capable of raising floating-point exceptions, and the conditions under which these exceptions may occur. The following chapters will focus almost exclusively on SWA exceptions, but the reason for presenting all the floating-point exceptions in the beginning is that SWA requests are floating-point exceptions themselves (even though not user visible), and because they can be combined with, or immediately followed by other floating-point exceptions.

## intel

## Conditions Causing, and Responses to, Floating-point Exceptions 3

The Itanium processor arithmetic instructions, most of which can cause floating-point exceptions, are listed in Table 3-1 (the only arithmetic instruction that cannot raise floating-point exceptions is *fcvt.xf*, which converts a signed integer value to register file floating-point format).

#### Table 3-1. Itanium<sup>™</sup> Processor Floating-point Arithmetic Instructions and Floating-point Exceptions which may be Raised

| FP Instructions | Exceptions   |                    |  |

|-----------------|--------------|--------------------|--|

|                 | Faults       | Traps              |  |

| fma             | V, D, SWA    | O, U, I, SWA       |  |

| fnorm           | V, D, SWA    | O, U, I, SWA       |  |

| fpma            | V, D, SWA    | O, U, I, SWA       |  |

| fms             | V, D, SWA    | O, U, I, SWA       |  |

| fpms            | V, D, SWA    | O, U, I, SWA       |  |

| fnma            | V, D, SWA    | O, U, I, SWA       |  |

| fpnma           | V, D, SWA    | O, U, I, SWA       |  |

| fmax            | V, D, SWA    |                    |  |

| fpmax           | V, D, SWA    |                    |  |

| fmin            | V, D, SWA    |                    |  |

| fpmin           | V, D, SWA    |                    |  |

| famax           | V, D, SWA    |                    |  |

| fpamax          | V, D, SWA    |                    |  |

| famin           | V, D, SWA    |                    |  |

| fpamin          | V, D, SWA    |                    |  |

| fcmp            | V, D, SWA    |                    |  |

| fpcmp           | V, D, SWA    |                    |  |

| fcvt.fx         | V, D, SWA    | 1                  |  |

| fpcvt.fx        | V, D, SWA    | 1                  |  |

| fcvt.xf         |              |                    |  |

| frcpa           | V, Z, D, SWA | O,U,I <sup>a</sup> |  |

| fprcpa          | V, Z, D, SWA |                    |  |

| frsqrta         | V, D, SWA    | la                 |  |

| fprsqrta        | V, D, SWA    |                    |  |

a. The traps indicated for frcpa and frsqrta cannot be generated directly by the hardware, but they can be raised by the IA-64 Floating-point Emulation Library, following a SWA fault for these instructions.

Among the instructions that are pseudo-ops, only *fnorm* is included, as it requires special attention. It is important to know that

$$fnorm.pc.sffl = f3$$

is equivalent to

$$fma.pc.sffl = f3, F1, F0$$

where F1 contains +1.0, F0 contains +0.0, and f1 and f3 are any other floating-point registers (f3 can also be F1 or F0). It is not equivalent to an *fina* instruction using another combination of registers, e.g.

$$fma.pc.sffl = F1, f3, F0$$

For example, assuming that the denormal exceptions are disabled, the instruction above would raise a SWA fault for any unnormal operand with a non-zero exponent, while the former (equivalent to an *fnorm*) would not. The instruction

$$fma.pc.sffl = f3$$

, F1, F0

will raise a SWA fault only if f3 is unnormal and its biased exponent in floating-point register file format is 0, or if f3 is unnormal and the denormal faults are enabled (the same holds for *fms.pc.sff1* = f3, F1, F0 and *fnma.pc.sff1* = f3, F1, F0). By contrast,

$$fma.pc.sffl = F1, f3, F0$$

will raise a SWA fault if f3 is unnormal (regardless of its exponent, or of the denormal exceptions being disabled or not).

As noted, the similar statements hold for *fms* and *fnma*, i.e. the *fms* and *fnma* instructions follow the same conventions for software assistance as *fma*. For example,

$$fms.pc.sffl = f3$$

, F1, F0

acts like an fnorm.

The other pseudo-ops that are not included in the list above are *fadd*, *fcvt.xuf*, *fmpy* (pseudo-ops of *fma*), *fnmpy* (pseudo-op of *fnma*), *fpmpy* (pseudo-op of *fpma*), *and fsub* (pseudo-op of *fnma*). Their floating-point exception behavior follows that of the instructions they are derived from, with one exception: if *fma*, *fms*, *fnma*, *fpma*, *fpms*, or *fpnma* raise a SWA fault and f2 is F0 (as in *fma.pc.sf f1* = *f3*, *f4*, F0), then the add operation in the multiply-add has to be skipped (the result has to be the IEEE result for a multiply operations, and if the product f3 \* f4 is 0.0 in absolute value, then adding or subtracting 0.0 might change the sign of the result).

Note that only Invalid (V), Divide-by-Zero (Z), Overflow (O), Underflow (U), and Inexact (I) are IEEE exceptions. Denormal/Unnormal (D) exceptions are specific to the IA-32 architecture and to the IA-64 architecture, and SWA faults and traps are IA-64 specific. Note also that the invalid exceptions, identified by "V" here might be denoted by "I" in other documents, and the inexact exceptions identified by "I", might be denoted by "P" (for "precision").

In the following, references will often be made to the Floating-point Status Register, or FPSR (Application Register 40), and to the Interrupt Status Register code, or ISR code (the ISR is Control Register 17). Their definitions are included here too (but complete descriptions are given in [1]).

### 3.1 The Floating-point Status Register

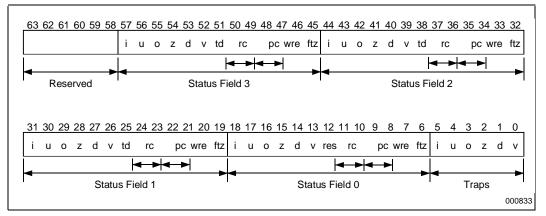

The Floating-point Status Register (Application Register 40) contains the dynamic control and status information for floating-point operations. There is one main set of control and status information (FPSR.sf0) and three alternate sets (FPSR.sf1, FPSR.sf2, and FPSR.sf3). The FPSR layout is shown in Figure 3-1.

Figure 3-1. Floating-point Status Register (AR40)

inte

Control bits 0 through 5 contain mask bits for floating-point exceptions (invalid, denormal, divide-by-zero, overflow, underflow, and inexact). If a mask bit is set, it disables the corresponding exceptions regardless of the status field being used.

Each of the four status fields contains seven control bits (ftz - flush-to-zero, wre - widest range exponent, pc - 2 bits for precision control, rc - 2 bits for rounding control, td - traps disabled [this bit is reserved in status field 0]), and six status flags (invalid, denormal, divide-by-zero, overflow, underflow, and inexact). Provided the underflow exceptions are disabled, the flush-to-zero mode (ftz = 1) causes tiny results to be truncated to the correctly signed zero, and the status flags for underflow and inexact exceptions to be set. The widest range exponent bit, wre, when set, specifies that the 17-bit exponent range will be used for floating-point calculations. The pc field specifies the dynamic precision for floating-point calculations (pc = 00 for 24-bit significands, pc = 10 for 53-bit significands, and pc = 11 for 64-bit significands). The rc field determines the rounding mode (rc = 00 for rounding to nearest, rc = 01 for rounding to negative infinity, rc = 10 for rounding to status fields 1, 2, and 3), disables the invalid, denormal, divide-by-zero, overflow, underflow, and inexact exceptions using the corresponding status field. For status field 0, or when td = 0 for status fields 1, 2, or 3, control bits 0 through 5 in the FPSR determine which floating-point exceptions are masked.

#### 3.2 The Interruption Status Register

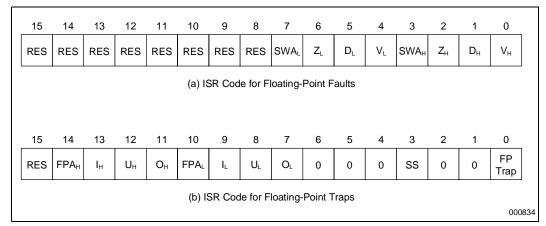

The Interruption Status Register (Control Register 17) receives information related to the nature of an interruption. Its lower 16 bits contain the ISR code, providing additional information specific to the current interruption. For unmasked floating-point exceptions, the ISR code contains the only indication for the cause of the interruption.

Figure 3-2 (a) shows the ISR code for floating-point faults. Only the lower eight bits are defined. Bits 0 through 3 (V - invalid operation, D - denormal operand, Z - divide-by-zero, SWA - software assistance) refer to floating-point faults raised by scalar instructions, or by the high order components of parallel (SIMD - Single Instruction, Multiple Data stream) instructions. Bits 4 through 7 (V, D, Z, SWA) refer to floating-point faults raised by the low order components of parallel instructions.

Figure 3-2 (b) shows the ISR code for floating-point traps. Bit 0 (FP TRAP) is always 1, indicating a floating-point trap. Bit 3 (SS) indicates a single-step trap. Bits 7 through 10 (O - overflow, U - underflow, I - inexact, FPA) refer to floating-point traps raised by the low order components of parallel instructions. Bits 11 through 14 (O, U, I, FPA) refer to floating-point traps raised by scalar instructions, or by the high order components of parallel instructions. The FPA bit indicates that the significand is larger in absolute value than the significand of the infinitely precise result. Note that there is no bit in the ISR code to indicate the occurrence of a SWA trap. There is no ambiguity though - the SWA handler can detect this situation by examining the ISR code bits for traps and the FPSR exception bits that mask/unmask floating-point exceptions.

Figure 3-2. Interruption Status Register Code (ISR.code) from ISR (CR17)

#### 3.3 Floating-point Exception Priority

The floating-point exception priority on the Itanium processor is the following:

- 1. NaTVal operand (not an exception, but handling this case has priority over floating-point exceptions).

- 2. Software Assistance (SWA) Floating-point Exception fault, Itanium processor specific, when one or more operands are unnormal (with the restrictions specified in Table 3-2 of Section 3.4).

- 3. Invalid Operation (V) Floating-point Exception fault due to one or more operands being in an unsupported format.

- 4. Invalid Operation (V) Floating-point Exception fault due to one or more operands that are signaling NaN (SNaN) (or QNaN for certain types of floating-point compare).

- 5. QNaN operand (not an exception, but handling this case has priority over lower-priority floating-point exceptions).

- 6. Invalid Operation (V) Floating-point Exception fault due to any reason other than those mentioned above (e.g. when executing frcpa for 0/0, or frsqrta for -Inf).

- 7. Zero Divide (Z) Floating-point Exception fault.

- 8. Denormal/Unnormal Operand (D) Floating-point Exception fault.

- 9. Software Assistance (SWA) Floating-point Exception fault, architecturally mandated (only for frcpa and frsqrta, when the exponents of the input operands satisfy certain conditions see Chapter 4).

- 10. Software Assistance (SWA) Floating-point Exception trap: when an fma, fpma, fms, fpms, fnma, or fpnma operation has a tiny result, the underflow exceptions are disabled, and the flush-to-zero mode is not enabled.

- 11. Numeric Overflow (O) and Underflow (U) Floating-point Exception traps (inexactness can also be indicated in the ISR.code field).

- 12. Inexact (I) Floating-point Exception trap.

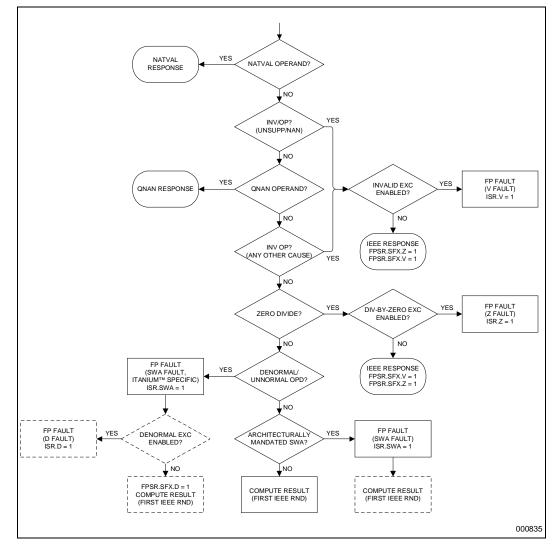

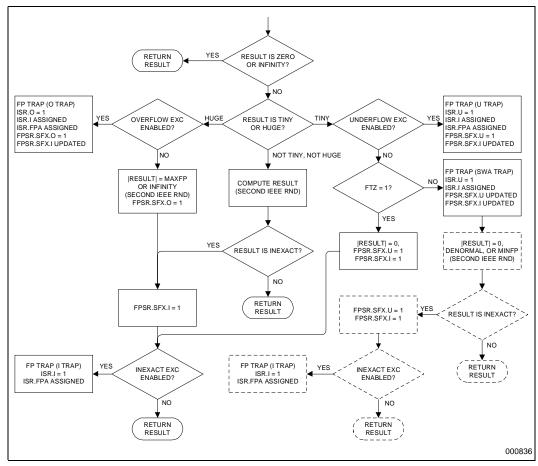

This list reflects the fact that the IA-64 architecture asks for SWA faults that are not architecturally mandated to be checked for prior to any other exceptions. For the Itanium processor though, these SWA faults will not occur if any invalid or divide-by-zero faults are raised (besides NaTVal or QNaN operands that do not cause invalid faults). Thus the "true" floating-point exception priority on the Itanium processor is illustrated in Figure 3-3 for faults, and Figure 3-4 and Figure 3-5 for traps. In both figures, the diamond shaped blocks are for decisions, the rectangular shaped blocks represent intermediate states, and the rectangular shaped blocks with rounded corners represent terminal states. The components represented with dotted lines correspond to software actions, while the rest are carried out directly by the processor hardware.

Figure 3-3, Figure 3-4 and Figure 3-5 apply to scalar floating-point instructions. For parallel instructions, two faults or two traps may occur simultaneously. In such cases, both faults or traps are reflected through bits set in the ISR register or in the appropriate status field of the FPSR register. Priorities are established on each half independently, but a fault in one half will have to be handled before a trap in the other half.

Note that the FPSR status flags are not updated when an umasked fault occur, and no result is provided to the exception handler. The status flags are updated on an unmasked trap (the exception handler will see the modified status bits in the appropriate status field of the FPSR) and a result is also provided to the exception handler. This is different from the IA-32 case, where status flags in the status word are updated for both unmasked floating-point faults and unmasked floating-point traps. In both cases of unmasked faults or traps, the cause of the exception is indicated by bits set in the ISR code.

If two floating-point faults or traps of the same kind (unmasked or not) occur in the two halves of a parallel instruction, the corresponding status flag in the FPSR can be viewed as a logical "OR" of the two hypothetical status flags for the individual halves (thus if a status flag is set when the exceptions are masked, one cannot tell whether the cause was in the low or in the high half of the instruction). For unmasked exceptions raised by parallel instructions, the FPSR has to be viewed in the same way, but the ISR code (as seen in Section 3.2 above) has separate sets of bits identifying exceptions in the low and the high halves.

The flowchart in Figure 3-3 starts after the input operands have been read. It includes also the cases of NaTVal and NaN operands (not exceptions, but fitting as priority among floating-point exceptions). In this figure, "IEEE Response" does not apply literally to all the instructions, as not all have their behavior specified in the IEEE standard. When this is the case, behavior following the spirit of the standard is defined for each Itanium processor instruction. The flowchart in Figure 3-3 ends with the computation of the result corresponding to the "first IEEE rounding" as specified in the IEEE Standard 754-1985 [6] (again, this does not apply literally to all the instructions), i.e. the result rounded to the destination precision, but with unbounded exponent. Special cases worth mentioning are those when the result of the *frcpa* and *frsqrta* instructions is computed in software following an Itanium processor specific SWA fault (in the leftmost of the three final states marked "COMPUTE RESULT" in Figure 3-3): if any input argument is unnormal and the mathematical conditions for the architecturally mandated SWA faults (see Table 3-2 of Section 3.3) are not met, then only an 11-bit reciprocal approximation value is returned, that will

allow computation by a compiler-inlined instruction sequence of the result for the divide or square root operation.

There is one exception to the flowchart in Figure 3-3: the frsqrta and fprsqrta instructions applied to a negative non-zero unnormal argument (this includes negative non-zero denormal values) does not signal an invalid fault directly. Instead, an Itanium processor specific SWA fault is raised. If the invalid exceptions are disabled (masked), the QNaN Indefinite value is returned. If the invalid exceptions are enabled (unmasked), an invalid fault is raised.

Note that in the process of computing the result of an instruction (when no unmasked floating-point fault exception occurs, or following a SWA fault), floating-point traps may be raised. This computation may be initiated in hardware, or in software when it follows a SWA fault.

Figure 3-3. Exception Priority for Itanium™ Processor Floating-point Faults

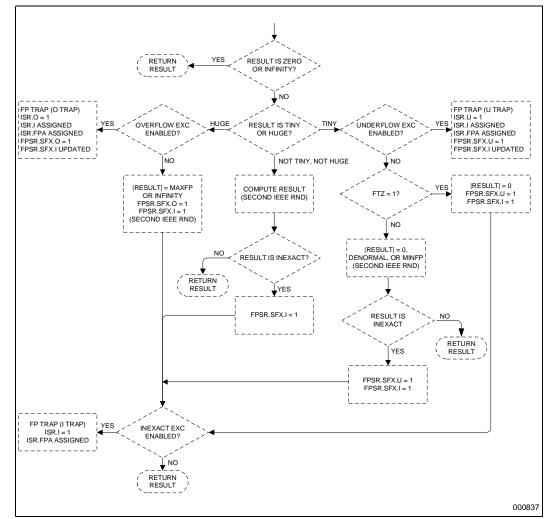

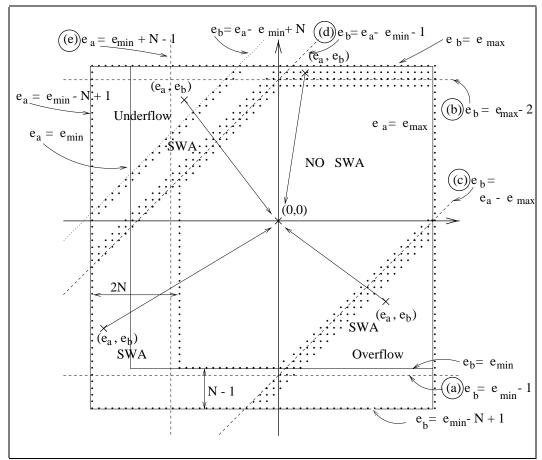

The flowchart in Figure 3-4 applies to the case when the result of the first IEEE rounding (as shown in Figure 3-3) was computed in hardware. The result is tested for zero or infinity, and then for tininess or hugeness. The result is tiny if its exponent satisfies  $e < e_{min}$ , and it is huge if  $e > e_{max}$ . In Figure 3-4 (and Figure 3-5 too), assigning to an ISR bit (e.g. in "ISR.I ASSIGNED") means setting it to 0 or 1, as appropriate for the operation it refers to. Updating an FPSR bit (e.g. in

"FPSR.SFX.I UPDATED") means performing a logical OR between the old value of the status flag bit in the user status field of the FPSR, and the value of the status flag (e.g the inexact status flag bit) for the current operation.

If the computation of the result of the first IEEE rounding operation shown in Figure 3-3 was performed in software (following a floating-point SWA fault), then the exception priority for floating-point traps is that depicted in Figure 3-5.

In both Figure 3-4 and Figure 3-5, the "second IEEE rounding" has as a result a value rounded to the destination precision and with bounded exponent range. Special cases of the second IEEE rounding can be those when the result is the correctly signed zero, denormal, smallest normal floating-point value, largest normal floating-point value, or infinity. The second IEEE rounding (for the instructions where this is applicable) starts with the result of the first IEEE rounding (plus a few additional bits of information - rounding mode, and round and sticky bits from the first IEEE rounding), and is not based on the values of the input operands.

## Figure 3-4. Exception Priority for Itanium<sup>™</sup> Processor Floating-point Traps Generated by a Hardware Initiated Computation of the Result

Figure 3-5. Exception Priority for Itanium™ Processor Floating-point Traps Generated by a Software Initiated Computation of the Result

For SWA traps, unmasked underflow traps, and unmasked overflow traps, the exception handler (the IA-64 Floating-point Emulation Library for SWA traps, or a user handler otherwise) receives the result after the first IEEE rounding, with exponent truncated to 17 bits. For unmasked inexact traps, the exception handler receives the result after the second IEEE rounding (which can include the special cases of a correctly signed zero, denormal, smallest normal floating-point number, largest floating-point number, or infinity).

Note that if an enabled floating-point fault is taken, no status flag is updated in the FPSR, and no result is provided to the exception handler. If an enabled floating-point trap is taken, the appropriate status flags are updated in the FPSR, and a result is provided to the exception handler. (The way the status flags are being set is different from the IA-32 behavior, where status flags are updated in the status word on any enabled floating-point exception.) In both cases (enabled faults or traps), the cause of the exception is indicated by bits set in the ISR code.

Conditions Causing, and Responses to, Floating-point Exceptions

## intel

## 3.4 Conditions Causing Floating-point Exceptions on the Itanium<sup>™</sup> Processor

The conditions under which floating-point exceptions occur for each Itanium processor arithmetic instruction are listed in Table 3-2 below. This table applies to both disabled and enabled exceptions. Note that SWA requests (faults or traps) are always "enabled" - there is no way to disable them. It is assumed that NaTVal values are filtered in advance. It is also assumed throughout this document that the qualifying predicate of any instruction being discussed is set to 1. For both disabled and enabled exceptions, the response is as specified by, or in the spirit of the IEEE Standard 754-1985 for Binary Floating-point Computations [3] (but note that the standard does not specify the behavior for certain operations such as fused multiply-add or min and max).

Note also that for parallel instructions, the single precision format does not allow for unsupported operands.

*Note:* In Table 3-2, exceptions, and the conditions causing them, are listed in the decreasing order of priority. For parallel instructions, it will be considered from now on that the low part is evaluated first, followed by the high part (this is just a convention, and is not imposed by the architecture).

| Floating-point Instruction                                                           | Exception                                 | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| fma.pc.sf f1 = f3, f4, f2<br>fms.pc.sf f1 = f3, f4, f2<br>fnma.pc.sf f1 = f3, f4, f2 | SWA fault, Itanium™<br>processor specific | Any unnormal operand, and no operand is unsupported, and no operand is a NaN, and the operation does not lead to (Inf -Inf), (-Inf + Inf), Inf * 0, Inf * (-0), -Inf * 0,<br>-Inf * (-0), 0 * Inf, -0 * Inf, 0 * (-Inf),<br>or -0 * (-Inf)                                                                                                                                                                                                                                                |

|                                                                                      | V                                         | Any unsupported operand, or any SNaN operand, or no NaN<br>operand and the operation leads to (Inf -Inf), (-Inf + Inf), Inf * 0, Inf *<br>(-0),<br>-Inf * 0, -Inf * (-0),<br>0 * Inf, -0 * Inf, 0 * (-Inf), or -0 * (-Inf)                                                                                                                                                                                                                                                                |

|                                                                                      | D                                         | Any unnormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                      | SWA trap, Itanium processor specific      | Result tiny, the underflow traps are disabled, and the flush-to-zero mode is not enabled                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                      | 0                                         | Result huge                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                      | U                                         | Result tiny if underflow exceptions are enabled; result tiny and<br>inexact if the underflow exceptions are disabled; the latter case will<br>occur directly from the hardware only if the flush-to-zero mode is<br>enabled, otherwise it would have already generated a SWA trap                                                                                                                                                                                                         |

|                                                                                      | I                                         | Result inexact                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| fnorm.pc.sf f1 = f3                                                                  | SWA fault, Itanium<br>processor specific  | Unnormal operand, and (biased exponent in floating-point register file format is 0 or denormal exceptions are enabled), and the operand is not unsupported, and the operand is not a NaN. Note that in floating-point register file format, an unnormal with a biased exponent of 0 is equivalent to the same unnormal with the biased exponent of 0xc001 (0xc001 = 0xffff - 0x3ffe), which corresponds to an unbiased decimal exponent of -16382, the minimum value for 15-bit exponents |

|                                                                                      | V                                         | Unsupported operand, or SNaN operand                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                      | D                                         | Unnormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                      | SWA Trap, Itanium processor specific      | Result tiny, the underflow traps are disabled, and the flush-to-zero mode is not enabled                                                                                                                                                                                                                                                                                                                                                                                                  |

#### Table 3-2. Conditions that Determine Occurrence of Floating-point Exceptions

| Floating-point Instruction                                                                     | Exception                                | Condition                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                | 0                                        | Result huge                                                                                                                                                                                                                                          |

|                                                                                                | U                                        | Result tiny if underflow exceptions are enabled; result tiny and inexact if they are disabled; the latter case will occur directly from the hardware only if the flush-to-zero mode is enabled, otherwise it would have already generated a SWA trap |

|                                                                                                | T                                        | Result inexact                                                                                                                                                                                                                                       |

| fpma.pc.sf f1 = f3, f4, f2<br>fpms.pc.sf f1 = f3, f4, f2<br>fpnma.pc.sf f1 = f3, f4, f2        | SWA fault, Itanium processor specific    | Any denormal operand, and no operand is a NaN, and the operation does not lead to (+Inf - Inf), (-Inf + Inf), Inf * 0, Inf * (-0),<br>-Inf * 0, -Inf * (-0), 0 * Inf, -0 * Inf,<br>0 * (-Inf), or -0 * (-Inf)                                        |

|                                                                                                | V                                        | Any SNaN operand, or no NaN operand and the operation leads to<br>(-Inf + Inf),<br>(-Inf + Inf), Inf * 0, Inf * (-0), -Inf * 0,<br>-Inf * (-0), 0 * Inf, -0 * Inf, 0 * (-Inf), or<br>-0 * (-Inf)                                                     |

|                                                                                                | D                                        | Any denormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                    |

|                                                                                                | SWA trap, Itanium processor specific     | Result tiny, the underflow traps are disabled, and the flush-to-zero mode is not enabled                                                                                                                                                             |

|                                                                                                | 0                                        | Result huge                                                                                                                                                                                                                                          |

|                                                                                                | U                                        | Result tiny if underflow exceptions are enabled; result tiny and inexact if they are disabled; the latter case will occur directly from the hardware only if the flush-to-zero mode is enabled, otherwise it would have already generated a SWA trap |

|                                                                                                | I                                        | Result inexact                                                                                                                                                                                                                                       |

| fmax.sf f1 = f2, f3<br>fmin.sf f1 = f2, f3<br>famax.sf f1 = f2, f3<br>famin.sf f1 = f2, f3     | SWA Fault, Itanium<br>processor specific | Any unnormal operand, and no operand is unsupported, and no operand is a NaN                                                                                                                                                                         |

|                                                                                                | V                                        | Any unsupported operand, or any NaN operand                                                                                                                                                                                                          |

|                                                                                                | D                                        | Any unnormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                    |

| fpmax.sf f1 = f2, f3<br>fpmin.sf f1 = f2, f3<br>fpamax.sf f1 = f2, f3<br>fpamin.sf f1 = f2, f3 | SWA Fault, Itanium<br>processor specific | Any denormal operand, and no operand is a NaN                                                                                                                                                                                                        |

|                                                                                                | V                                        | Any NaN operand                                                                                                                                                                                                                                      |

|                                                                                                | D                                        | Any denormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                    |

| fcmp.frel.fctype.sf p1, p2 = f2, f3                                                            | SWA Fault, Itanium processor specific    | Any unnormal operand, and no operand is unsupported, and no operand is a NaN                                                                                                                                                                         |

|                                                                                                | V                                        | Any unsupported operand, or any SNaN operand, or (any QNaN operand if 'frel' is one of It, le, nlt, nle)                                                                                                                                             |

|                                                                                                | D                                        | Any unnormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                    |

| fpcmp.frel.sf f1 = f2, f3                                                                      | SWA Fault, Itanium processor specific    | Any denormal operand, and no operand is a NaN                                                                                                                                                                                                        |

|                                                                                                | V                                        | Any SNaN operand, or (any QNaN operand if 'frel' is one of lt, le, nlt, nle)                                                                                                                                                                         |

| Table 3-2. Co | onditions that Determine ( | Occurrence of Floating | g-point Exceptions (Cont'd) |

|---------------|----------------------------|------------------------|-----------------------------|

|---------------|----------------------------|------------------------|-----------------------------|

| Table 3-2. | Conditions that Determine Occurrence of Floating-point Exceptions (Cont'd) |

|------------|----------------------------------------------------------------------------|

|            | <b>3</b>                                                                   |

| Floating-point Instruction                                                                             | Exception                                | Condition                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                        | D                                        | Any denormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                                                                                                                                 |

| fcvt.fx.sf f1 = f2<br>fcvt.fxu.sf f1 = f2<br>fcvt.fx.trunc.sf f1 = f2<br>fcvt.fxu.trunc.sf f1 = f2     | SWA Fault, Itanium<br>processor specific | Unnormal operand, and the operand is not unsupported, and the operand is not a NaN                                                                                                                                                                                                                                                                                |

|                                                                                                        | V                                        | Unsupported operand, or NaN operand, or input is too large in absolute value                                                                                                                                                                                                                                                                                      |

|                                                                                                        | D                                        | Unnormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                                                                                                                                     |

|                                                                                                        | I                                        | Result inexact                                                                                                                                                                                                                                                                                                                                                    |

| fpcvt.fx.sf f1 = f2<br>fpcvt.fxu.sf f1 = f2<br>fpcvt.fx.trunc.sf f1 = f2<br>fpcvt.fxu.trunc.sf f1 = f2 | SWA Fault, Itanium<br>processor specific | Denormal operand, and the operand is not a NaN                                                                                                                                                                                                                                                                                                                    |

|                                                                                                        | V                                        | Any NaN operand, or any input is too large in absolute value                                                                                                                                                                                                                                                                                                      |

|                                                                                                        | D                                        | Any denormal operand (not raised directly by the hardware, but following an Itanium processor specific SWA fault)                                                                                                                                                                                                                                                 |

|                                                                                                        | I                                        | Result inexact                                                                                                                                                                                                                                                                                                                                                    |

| frcpa.sf f1, p2 = f2, f3                                                                               | SWA fault, Itanium<br>processor specific | any unnormal operand, and no operand is unsupported, and no<br>operand is a NaN, and the operation is not Inf/Inf, and it is not<br>[pseudo]0/[pseudo]0, and it is not (non-zero normal)/[pseudo]0, and it<br>is not (non-pseudo 0 unnormal)/[pseudo]0 (with any combination of<br>signs; the square brackets indicate an optional component)                     |

|                                                                                                        | V                                        | Any unsupported operand, or any SNaN operand, or the operation is<br>Inf/Inf, or it is [pseudo]0/[pseudo]0<br>(with any combination of signs)                                                                                                                                                                                                                     |

|                                                                                                        | Z                                        | Operation is (non-zero normal)/[pseudo]0, or (non-pseudo 0<br>unnormal)/[pseudo]0 (with any combination of signs)                                                                                                                                                                                                                                                 |